## Maas Gilbert Cell Multiplier Measurements V: Chips from the second ("production") run

## A.I. Harris 2 July 2003

## 1 Overview and summary

GCS finished fabrication of the "production" run of four full wafers in mid-June. We received a total of 4904 multipliers with post-amps and 2112 multipliers without post-amps. In addition, we received approximately 20 calibration structures (open, short, match, thru), 40 bare HBTs, and 20 of each of three single-transistor test amplifiers for each of the four wafers.

A quick look at a sample of multipliers from all four wafers from 2 to 18 GHz shows that:

- The shape of the response vs. frequency curve is essentially the same as the prototype devices.

- The absolute responsivity (V/W) is lower than the prototype devices responsivity by about 3 dB.

• The output noise density is close to 3 dB lower than the prototype device noise. Combined, this means that the performance of the new chips in a correlator system would be nearly the same as for the prototype chips, although the reduced responsivity may cause an approximately 1 dB reduction in input power dynamic range.

## 2 Measurements

I used the same setup for measurements as for the prototype chips, and remeasured the prototypes I use here for comparison. The new and prototype run chips were on the same Gel Pak carrier in a Suess probe station. The -25 dBm input signals were from a synthesizer (set 33 kHz above the nominal frequency) and the cw output from a network analyzer. The difference frequency signal at the multiplier output level was measured with the peak-find mode of a low-frequency spectrum analyzer. With the RF power switched off, I used the same spectrum analyzer to measure the output noise voltage spectral density at 50 kHz.

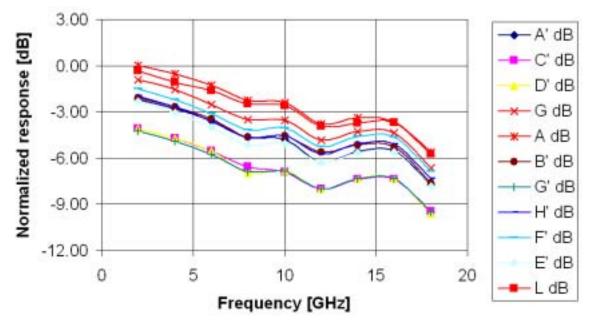

Figure 1 summarizes the measurements of response vs. frequency from 2 to 18 GHz for eleven devices: three from the prototype run and two each from the new wafers. The shapes are all very similar, but there is a clear trend for the new devices to have lower responsivity than the prototypes. The shape of the curve is somewhat different than the shape I had measured before: the peak near 4 GHz has been replaced by a generally smooth rolloff from low frequencies to high. I suspect that the previous peak may have been spurious, produced by a resonance in the N-SMA adaptor on the synthesizer, but there is no simple proof. The cable loss correction is unchanged from the prototype measurements.

Figure 1: Response vs. frequency for a sample of 11 multipliers. Multipliers without primes are from the prototype run; those with primes are two samples each from each wafer in the June 2003 run. The response of the three multipliers from the prototype run is above the response of the eight from the June fabrication.

The transistor gain seems to be lower in this run than in the prototype fabrication run, which may explain the drop in multiplier responsivity. Direct comparison of the single-device transistor amplifiers from the new and prototype fabrications shows a uniform gain drop of 0.6 dB for the amplifier without feedback (TEST3) and a uniform gain drop of 0.22 dB for the amplifier with input matching resistors and feedback (TEST1).

There is no change in the bias current between the prototype and new multiplier chips.

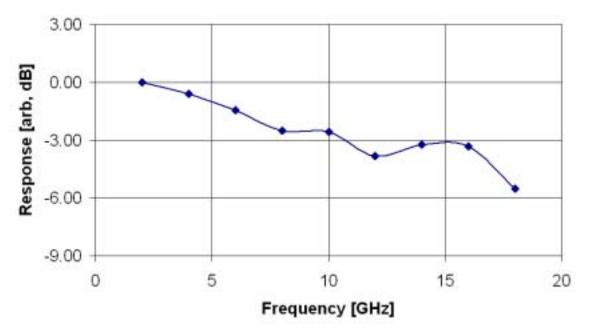

Figure 2 shows the averaged response vs. frequency. The 3 or 4 dB bandwidth extends to approximately 16 GHz. The responsivity of a typical device (E') is 32 V/mW at 2 GHz: 200 mV p-p for -25 dBm power at both inputs.

Figure 2: Representative multiplier response vs. frequency.

The lower responsivity will not be a problem in a correlator system if the output noise scales with the responsivity for these multipliers. The minimum power level needed to keep spectrometer noise well below receiver noise is

$$P_{in} = \frac{3S_V \sqrt{B}}{R} \quad , \tag{1}$$

where  $S_V$  is the voltage noise spectral density, B is the correlator bandwidth, and R is the multiplier responsivity.

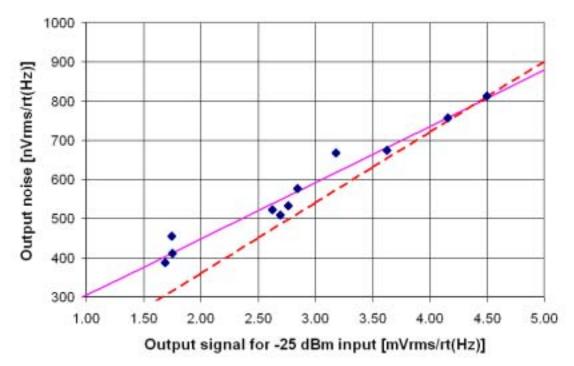

Figure 3 shows that the noise does scale with responsivity, although it decreases somewhat more slowly than the responsivity. The three highest points are from the prototype multipliers, with the remaining eight points are from the new devices. A fit to the noise vs. responsivity curve shows that the slope is shallower than a 1:1 scaling with responsivity and that there is a nonzero y-axis intercept. Bias voltage noise added negligibly to the output noise: there is no trace of the power supply's 4.5 kHz switching rate in the multiplier's output spectrum.

The result of the drop in responsivity is that the new chips will have a smaller input dynamic range, an approximately 1 dB effect.

Figure 3: Output noise vs. output signal, or responsivity, (points) for -25 dBm input power level. The solid line is a linear fit to the data and the dashed line would be perfect scaling of noise with response, normalized to the highest point. The noise decreases somewhat more slowly than the responsivity.